新闻中心

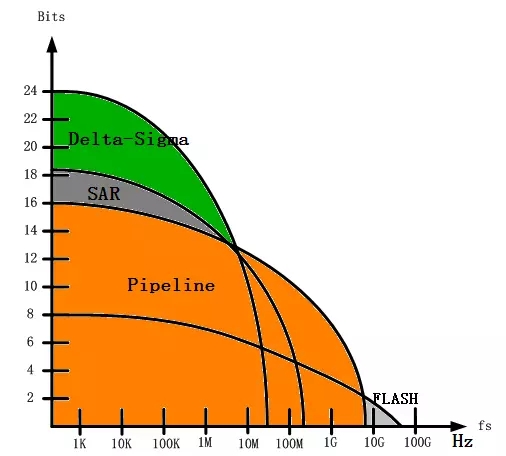

Sigma-Delta ADC是一种目前使用最为普遍的高精度ADC结构,在精度达到20位以上的场合,Sigma-Delta是必选的结构。通过采用过采样、噪声整形以及数字滤波技术,降低对模拟电路的设计要求,实现了其他类型的ADC无法达到的高精度和低功耗。通常情形下,各种类型ADC的精度与速度关系如图1所示。

图1 不同类型的ADC的精度和速度的对比

Sigma-Delta ADC的运作过程,就是把待测信号Vin与参考电压(±Vref)之间的差值进行不断的累积并通过反馈令这个差值趋于零。

实质上ADC就是除法器。

Dout=(Vin/Vref) * 2^n

一个分辨率为n位的ADC完成了一个以Vref为除数的除法,并且把结果用n位二进制数来表达。

那么什么是Sigma-Delta ADC?

Sigma-Delta最终实现的,与所有的ADC一样,就是完成除法。模拟集成电路中除法器是不可实现的,但是模拟电路可以非常好的实现加法和减法(用运放及模拟开关对电容进行充放电)。Sigma-Delta ADC正是用加法和减法去实现除法的一种方式。

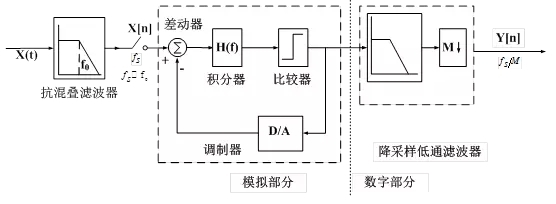

具体来说,如图2所示,Delta-Sigma ADC的工作原理是由差动器、积分器和比较器构成调制器,它们一起构成一个反馈环路。调制器以大大高于模拟输入信号带宽的速率运行,以便提供过采样。模拟输入与反馈信号(误差信号)进行差动(delta)比较。该比较产生的差动输出馈送到积分器(sigma)中。然后将积分器的输出馈送到比较器中。比较器的输出同时将反馈信号(误差信号)传送到差动器,而自身被馈送到数字滤波器中。

图2 过采样ADC结构图

这种反馈环路的目的是使反馈信号(误差信号)趋于零。比较器输出的结果就是1/0流。该流如果1密度较高,则意味着模拟输入电压较高;反之,0密度较高,则意味着模拟输入电压较低。接着将1/0流馈送到数字滤波器中,该滤波器通过降采样与抽样,将1/0流从高速率、低精度位流转换成低速率、高精度数字输出。

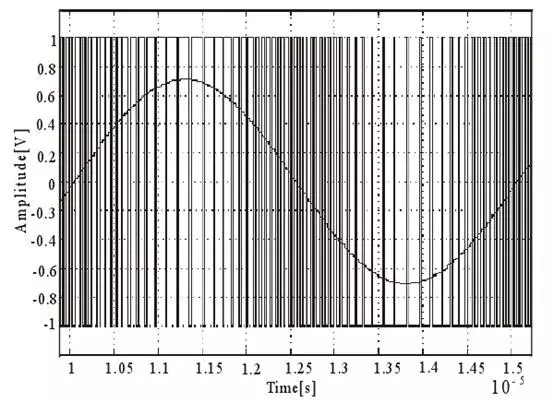

一个正弦波输入信号与比较器输出的码流所对应的波形如图3所示,输出码流随着输入信号幅值的变化而变化,当输入信号处于波峰位置时,输出码流1占大多数;当输入信号处于波谷位置时,输出码流0(图3中,以-1表示)占大多数;输入信号处于平衡位置时,输出码流1和0跳变激烈,各占50%。

图3 正弦信号幅度与比较器输出的码流所对应的波形

sigma-delta ADC也有不同的结构,其特点可以如表1所示。

表1 不同结构的Sigma-DeltaADC的对比

| 结构 | 优点 | 缺点 |

| 低阶、单环、一位量化 | 结构稳定、电路简单、输入范围大 | 精度较其他结构稍低 |

| 高阶、单环、一位量化 | 精度高、谐波小、电路简单 | 稳定性差、输入范围小 |

| 级联结构 | 精度高、电路简单、高稳定性 | 元件匹配性要求高、谐波大 |

| 多位量化 | 谐波小、精度高、功耗低 | 电路复杂、线性度差 |

湘潭芯力特电子科技有限公司(简称芯力特公司)是一家专业从事混合信号集成电路设计的高科技企业,有专业的ADC设计团队,全面考虑各种非理想因素对ADC性能带来的影响,可以为客户定制性能优异、多种类型的ADC。公司围绕智慧电网等物联网致力于相关芯片技术攻关,采用灵活的商务模式提供专门的人力、物力进行技术服务与产品的定制设计,以满足客户的专用型需求,以一站式的服务达到客户与自身双赢的目的。

芯力特公司有非常优秀的AD/DA设计能力,在硅片上成功研发过多种AD,DA芯片与IP:

1)高精度高速10bit 100MHz pipeline/12bit 60MHz pipeline的ADC,已经在0.18um/0.13um CMOS工艺验证;

2)高精度低速低功耗12bit 4MHz SAR ADC,已经在0.18um CMOS工艺验证;

3)高精度低速的sigma-delta ADC,从14-24bit,已经在0.5um/0.35um/0.18um CMOS工艺验证;

4)极高速的200MHz 6-8bit flash ADC,已经在0.18um/0.13um CMOS工艺验证;

5) 8/10/12bitDAC,已经在0.35um/0.25um/0.18um/0.13umCMOS工艺验证。

联系方式:

联系人:张文杰

电话:18502537108

Email:[email protected]

网址:

长按二维码关注“芯力特”微信号

地址:湖南省长沙高新开发区尖山路39号中电软件园总部大楼

上海:上海市浦东新区豪威科技园区上科路88号

深圳:深圳市南山区科技园高新南七道1号粤美特大厦24楼

业务:15074991500(华东区),13647318510(华南区),15673115977(北西区)

Copyright © 2020 湖南芯力特电子科技有限公司 湘ICP备2022017381号