新闻中心

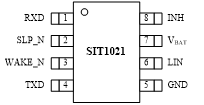

SIT1021具有超低功耗休眠模式,芯片在休眠模式下,流过VBAT脚电流典型值仅为3uA;SLP_N脚控制芯片进入正常工作模式和休眠模式,当SLP_N脚为高电平时,芯片进入正常工作模式;当SLP_N脚为低电平时,芯片进入休眠模式;SLP_N脚内置弱下拉(国外同类芯片一样内置弱下拉),较容易受外界干扰影响,上电后用手触摸此管脚能够引起芯片进入正常工作模式;这样如果在干扰比较强的应用环境中SLP_N端口可能会受干扰被误触发,造成功能不良。SIT1021管脚图如下:

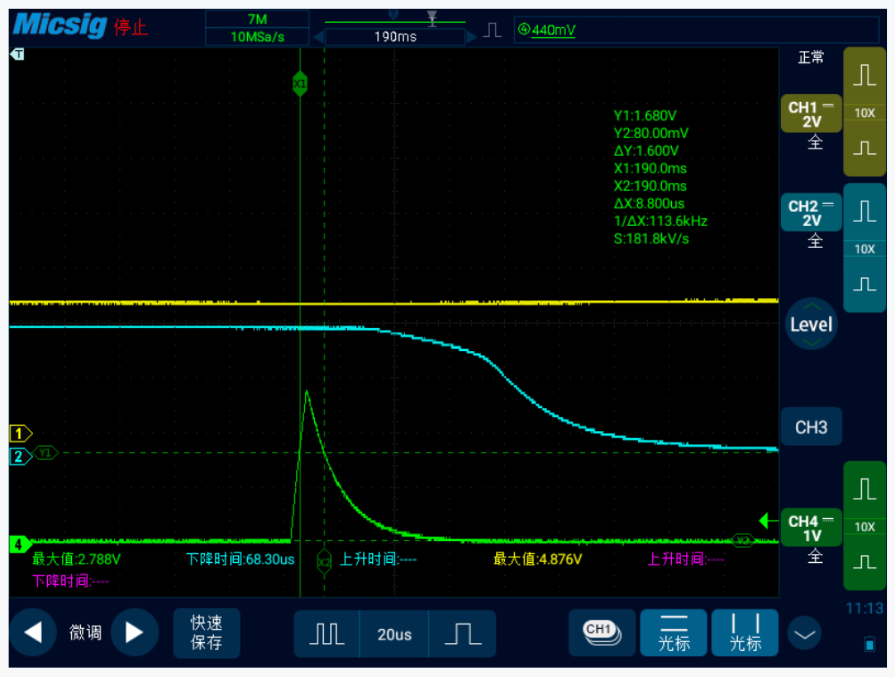

有客户在使用SIT1021时发现,上电瞬间SLP_N端口有一个幅值为2.8V尖峰电压,导致芯片由上电模式进入休眠模式,如下图(绿色通道为SLP_N脚波形、蓝色通道为INH脚波形):

测量此尖峰电压,超过2V幅值的电压持续时间为6us左右,满足芯片由上电模式进入正常工作模式高电平要求(高电平阈值为2V~7V,持续时间2us~10us),当干扰尖峰过后,SLP_N被拉低从而进入休眠模式,导致INH脚关闭输出,控制MCU供电的LDO使能脚被置低,关闭输出,MCU掉电;不能收发数据,导致功能异常(国外同类芯片也会出现此现象)。解决方法为:在SLP_N脚对GND并联一个470nF~1uF电容滤波,将干扰幅值滤波到SLP_N低电平阈值以下(阈值为-0.3V~0.8V),下图是在SLP_N并联470nF电容后干扰的波形:

干扰幅值(绿色通道)由原来的2.8V降低为0.33V左右,此时INH(蓝色通道)输出高,各功能均能正常工作。

此外为了加强芯片的抗干扰能力,可在芯片VBAT脚对GND脚接一个100nf电容和一个大容量电容,也可以在VBAT上串一个磁珠。

地址:湖南省长沙高新开发区尖山路39号中电软件园总部大楼

上海:上海市浦东新区豪威科技园区上科路88号

深圳:深圳市南山区科技园高新南七道1号粤美特大厦24楼

业务:15074991500(华东区),13647318510(华南区),15673115977(北西区)

Copyright © 2020 湖南芯力特电子科技有限公司 湘ICP备2022017381号